## **Electronic Chemicals**

# Honeywell

Honeywell Polish Etch I and II for Wafer Thinning

### Honeywell **Polish Etch** I and II

#### WAFER THINNING MATERIALS

#### **APPLICATIONS**

- Used as a contour etch to delineate cracks and scratches; typical etch depth is 0.0003 inch (7µm)

- Relieves wafer box and eliminates stress related breakage due to scratches created with grinding

#### **OVERVIEW**

Honeywell's wafer thinning materials are part of three new product lines (wafer thinning materials, performance cleans, selective etchants) being introduced from its state-of-the-art electronic chemicals manufacturing sites in Chandler, Arizona and Seelze, Germany.

### Honeywell's electronic chemicals manufacturing site in Chandler, Arizona.

These customized, application specific offerings provide improved cost of ownership (CoO), increased yield and ease-ofuse. Our application expertise maximizes customer wafer thinning processes with application development support and troubleshooting know-how while our consistent drum-to-drum and bottle-to-bottle wafer etching characteristics provide unsurpassed batch-to-batch product uniformity. A robust manufacturing infrastructure and application expertise further enable Honeywell to deliver flexible end products, custom-matched to the best chemistry formulations for customer processes and specifications.

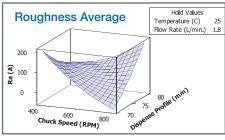

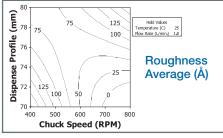

#### (mm) 125 100 Profile 76 Roughness nse Average (Å) 125 100 600 500

**RESEARCH AND**

DEVELOPMENT

**ETCHER**

**PARAMETER**

Temperature (°C)

Chuck Speed (RPM)

Flow Rate (L/min.)

Dispense Profile (mm)

tool).

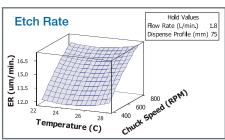

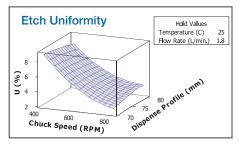

Honeywell and SEZ developed and per-

formed an extensive design of experiment

(DOE) to identify the critical chemical and

operating parameters necessary to maxi-

post-grinding, etch uniformity and surface

SETTING

Middle

25

600

1.8

75

Low

22

400

1.6

70

High

800

2.0

A stable etch process and consistent

etchant are needed to ensure a stable

wafer backside etching process

Conclusions of this work indicate:

• Post etch surface roughness is pri-

marily a function of the chuck speed

morphology of a stress removal process (utilizing a SEZ single wafer processing

mize stress reduction associated with

### **Honeywell Electronic Materials**

USA: 1-509-252-2102 China: 86-21-28942481 **Germany:** 49-5137-999-9199 Japan: 81-3-6730-7092 Korea: 82-2-3483-5076 Singapore: 65-6580-3593 Taiwan: 886-3-6580300 ext.312

www.honeywell.com/sm/em

Although all statements and information contained herein are believed to be Atthough all statements and information contained nerein are believed to be accurate and reliable, they are presented without guarantee or warranty of any kind, express or implied. Information provided herein does not relieve the user from the responsibility of carrying out its own tests and experiments, and the user assumes all risks and liability for use of the information and results obtained. Statements or suggestions concerning the use of materials and processes are made without representation or warranty that any such use is free of catent infringement and are not recommendations to infringe any nater. The patent infingement and are not recommendations to unusual patent user should not assume that all toxicity data and safety measures are indicated user should not assume that all toxicity data and safety measures are indicated. PB1171011Rev8 patent infringement and are not recommendations to infringe any patent. The ©2011 Honeywell International Inc.